การ interupt ใน 8051

ประเภทของการ interrupt

-

External interrupt การตรวจสอบสัญญาณที่มา

interrupt นี้

จะสามารถกำหนดให้มีการตรวจสอบใน

ลักษณะเมื่อได้มีการเปลี่ยนแปลงระดับสัญญาณ

(Level-sensitive) ไปแล้ว

หรือในช่วงเวลาขณะเริ่มมี

การเปลี่ยนแปลง

สัญญาณจาก logic สูงไปต่ำ (

Edge-sensitive )

-

Internal inetrrupt

แหล่งกำเนิดสัญญาณนี้จะเป็นวงจรภายใน

Microcontroller เอง เช่น วงจรนับ

/จับเวลา

วงจรเชื่อต่อสัญญาณอนุกรม เป็นต้น

โครงสร้างการ

interrupt เกิดได้ 5

ลักษณะ คือ

- INT0

สัญญาณ interrupt

จากภายนอก ทางขาสัญญาณ

P3.2 โดย 8051 จะทำการสุ่มตัวอย่าง

สัญญาณ

เมื่อสิ้นสุดทุก Machine Cycle

- INT1

สัญญาณ interrupt จากภายนอกทางขาสัญญาณ P3.3 โดย 8051

จะทำการสุ่มตัวอย่าง

สัญญาณเมื่อสิ้น

สุดทุก Machine Cycle

- Timer0

สัญญาณการเกิด Overflow ของ Timer 0

- Timer1

สัญญาณการเกิด Overflow ของ Timer 1

- Serial

Port การเกิด interrupt

ที่เกิดขึ้นจาการรับ/ส่งข้อมูลอนุกรม

ทำให้มีผผผลต่อ flag interrupt RI และ TI

ตามลำดับ

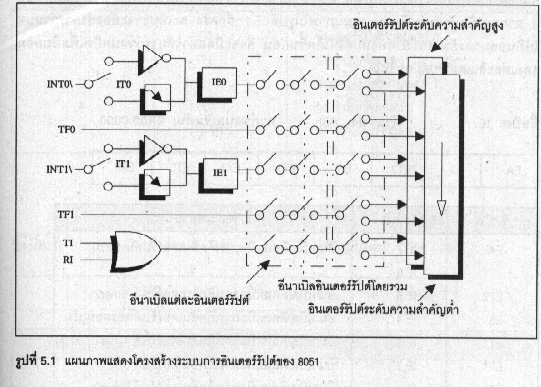

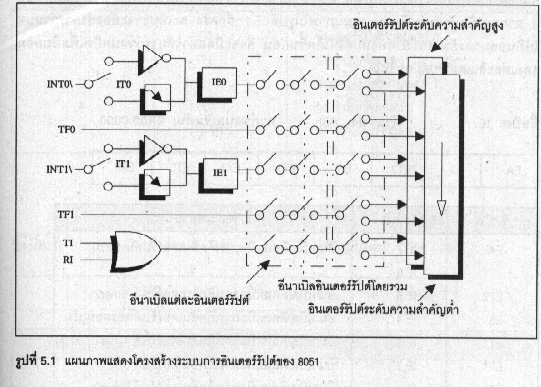

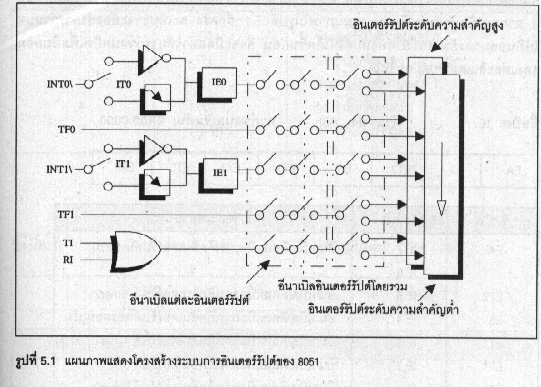

จากแผนภาพโครงสร้างระบบ

interrupt ของ 8051 จะเห็นว่าเมื่อเกิดการ interrupt

สัญญาณ ต่างๆขึ้น

จะส่งผลให้มีการควบคุมเพื่อสั่งให้

processor กระโดดไปทำงานที่ต่ำแหน่ง Address

ต่างๆ ตามประเภทของแหล่งกำเนิด

สัญญาณ interrupt

ที่เกิดขึ้น ซึ่งปรกติควรมีการสร้าง program

เหล่านี้ไว้ เพื่อทำหน้าที่ย่อยบริการ

interrupt

การกำหนดให้

8051 สามารถตอบรับการ interrupt แต่ละประเภท

ทำได้โดยกำหนด bit ของ ข้อมูลที่เกี่ยวข้อง

ซึ่งมักอยู่ภายใน register TCON และ SCON

หากได้ว่ามีการกำหนด ค่าของ bit

ซึ่งอยู่ภายใน register IE ( Intereupt

Enable Register )

ด้วยแล้ว ก็สามารถตอบรับการ interrupt

ของสัญญาณนั้นๆ ได้

นอกจากหนี้ตามแผนภาพในรูป

ยังแสดง

ให้เห็นว่าสัญญาณ interrupt แต่ละ

ประเภท ยังสามารถกำหนด piority ของการ interrupt ได้ 2 ลักษณะ คือ

High Low

piority กล่าว

คือขณะที่ประมวลผลอยู่ภายในส่วนของ

program ย่อย บริเวณ interrupt ของสัญญาณที่มีระดับความ

สำคัญ

ต่ำอยู่ ก็สามารถถูก interrupt ที่มี

piorrity สูงกว่าได้ แต่หากว่าเป็นสัญญาณ interrupt

ที่มี piority

เดียวกันหรือต่ำกว่าแล้วก็

จะต้องรอให้เสร็จสิ้นการประมวลผลที่ดำเนินอยู่ก่อน

การควบคุม interrupt

ตามโครงสร้างที่ด้านการจัดการ

interrupt ของ 8051

สามารถกำหนดเรียกเพื่อยินยอมหรือไม่ยิน

ยอม

(Enable/Disabble) ให้มีการ interrupt

แต่ละสัญญาณได้ โดยใช้วิธีการกำหนด ค่าของ

bit ภาย ใน register IE

[ บทเรียน ] [ 204471 ] [ รายวิชา ]

[ ภาควิชาวิศวกรรมคอมพิวเตอร์ ] [ คณะวิศวกรรมศาสตร์ ] [ มหาวิทยาลัยเกษตรศาสตร์ ]